Difference between revisions of "Digital-Electronics Obstacle Course"

| Line 24: | Line 24: | ||

| + | |||

| + | |||

| + | ---- | ||

=== Activities === | === Activities === | ||

| Line 30: | Line 33: | ||

# Read chapter 8 of Horowitz & Hill's ''The Art of Electronics''. | # Read chapter 8 of Horowitz & Hill's ''The Art of Electronics''. | ||

# Read Chapters 10 and 11 of Keith Brindley's eBook ''Starting Electronics''. | # Read Chapters 10 and 11 of Keith Brindley's eBook ''Starting Electronics''. | ||

| − | + | ==== The Inverter or NOT Gate ==== | |

# Using T1 = TIP31C, R = 10k, R2 = 1k, Vcc = 10VDC construct the circuit shown at the right. | # Using T1 = TIP31C, R = 10k, R2 = 1k, Vcc = 10VDC construct the circuit shown at the right. | ||

## Apply 0V to input A. What's the output Q? | ## Apply 0V to input A. What's the output Q? | ||

| Line 38: | Line 41: | ||

## Letting the input = A and the output = B write a Boolean statement describing this NOT gate (i.e., Q = ???). | ## Letting the input = A and the output = B write a Boolean statement describing this NOT gate (i.e., Q = ???). | ||

''We can also use the "True" and "False" representation of digital logic with a "0" state equated with a "False" value and "1" state equated with a "True" value.'' | ''We can also use the "True" and "False" representation of digital logic with a "0" state equated with a "False" value and "1" state equated with a "True" value.'' | ||

| + | ''Yet another digital logic representation is the "High" and "Low" representation equated with the "1" and "0" states respectively. | ||

| Line 45: | Line 49: | ||

| − | + | ==== The OR Gate ==== | |

| + | [[File:Orgate.png|right|200px|]] | ||

# Using two [[Media:2N4401BU.pdf| 2N4401BU]] transistors with R = 10k, R1 = 4.7k and Vcc = 6VDC construct the circuit shown at the right. | # Using two [[Media:2N4401BU.pdf| 2N4401BU]] transistors with R = 10k, R1 = 4.7k and Vcc = 6VDC construct the circuit shown at the right. | ||

## Apply 0V to A and 0V to B. What is Q? | ## Apply 0V to A and 0V to B. What is Q? | ||

| Line 64: | Line 69: | ||

| − | + | ==== The AND Gate ==== | |

| + | [[File:Andgate.png|right|200px]] | ||

# Using two [[Media:2N4401BU.pdf| 2N4401BU]] transistors with R = 10k, R1 = 4.7k and Vcc = 6VDC construct the circuit shown at the right. | # Using two [[Media:2N4401BU.pdf| 2N4401BU]] transistors with R = 10k, R1 = 4.7k and Vcc = 6VDC construct the circuit shown at the right. | ||

## Apply 0V to A and 0V to B. What is Q? | ## Apply 0V to A and 0V to B. What is Q? | ||

| Line 78: | Line 84: | ||

| − | + | ==== The NOR, NAND, XOR and XNOR Gates ==== | |

It should be clear that we could follow the OR gate with a NOT gate and get a NOT OR gate (a '''NOR''' gate). | It should be clear that we could follow the OR gate with a NOT gate and get a NOT OR gate (a '''NOR''' gate). | ||

| Line 87: | Line 93: | ||

An OR gate outputs "True" when either (or both) of its inputs is "True". However, an XOR gate outputs True (we'll drop the quotes) when either of its inputs is True (but not both). The XNOR gate is a combination of an XOR gate and an inverter (a NOT XOR gate). | An OR gate outputs "True" when either (or both) of its inputs is "True". However, an XOR gate outputs True (we'll drop the quotes) when either of its inputs is True (but not both). The XNOR gate is a combination of an XOR gate and an inverter (a NOT XOR gate). | ||

| − | It would be extremely tedious (though in principle possible) to build every logic circuit from discrete transistor elements. There are dedicated digital ICs that perform these logic functions. | + | ==== Digital ICs ==== |

| + | |||

| + | It would be extremely tedious (though in principle possible) to build every logic circuit from discrete transistor elements. There are dedicated digital ICs that perform these logic functions reducing cost, saving time and generally making it easier to build complex digital circuits. | ||

| + | |||

| + | * [http://en.wikipedia.org/wiki/List_of_7400_series_integrated_circuits The 7400 series digital ICs]. These are robust [http://en.wikipedia.org/wiki/Transistor%E2%80%93transistor_logic TTL] (transistor-transistor logic) devices and operate at 5V. | ||

| + | |||

| + | * [http://en.wikipedia.org/wiki/List_of_4000_series_integrated_circuits The 4000 series digital ICs]. These are (slightly less robust) [http://en.wikipedia.org/wiki/CMOS CMOS] devices and operate over a range of voltages. | ||

| + | |||

| + | ==== Bistable Circuits - [http://en.wikipedia.org/wiki/Flip-flop_(electronics) Flip-Flops] - Digital Memory ==== | ||

| + | The type of logic gates examined above are known as combinational (or time independent) logic gates. That is, their output is a | ||

| + | function (only) of their '''present combined''' inputs. This means that combinational logic has no memory. | ||

| + | |||

| + | For a circuit to have memory its output must depend not only on its present input '''but also on its past input'''. Logic of this type is known as sequential logic. Virtually all circuits in practical digital devices are a mixture of combinational and sequential logic.<br><br> | ||

| + | |||

| + | '''The SR-Type NOR Bistable or Latch''' | ||

| + | [[File:SRNORbistable.png|thumb|300px|The S-R NOR Bistable or Latch and Function Table]] | ||

| + | [[File:FlipFlopDiagram.PNG|thumb|right|300px| Flip-Flop Transistor Circuit]] | ||

| + | [[File:NORtt.gif|left|thumb| NOR Truth Table| 300px]] | ||

| + | Recall that the NOR gate is an inverting OR gate. Also recall that an OR gate's output is High when either or both of its inputs is High. So, a NOR gate's output is High when both its inputs are Low and its output is Low for all else. | ||

| + | |||

| + | Now consider the NOR latch symbolic circuit shown at the right with both S and R initially Low (S and R stand for Set and Reset respectively). If S then goes High the output of S-gate is Low. And since the output of the S-gate is cross-coupled to the input of the R-gate the R-gate is High. This High from the R-gate output is then fed back into the S-gate input keeping the S-gate output low. | ||

| + | |||

| + | Now consider what happens when S subsequently goes Low. Since the input to the S-gate is now still a combination of a Low and a High its output is still Low. That is, the output <math>\bar{Q}</math> is "latched" Low and Q is "latched" High regardless of subsequent changes in S. The outputs "remember" their states. The analysis remains valid when R and S are switched. | ||

| − | |||

| − | + | # Using a proto-board, two [[Media:2N4401BU.pdf| 2N4401BU]] transistors and LEDs build the flip-flop circuit shown at the right. | |

| + | ## Verify the S-R NOR latch function table. | ||

Revision as of 14:11, 17 February 2015

Contents

Permanent Materials (located in the electronics area):

- power supplies

- function generators

- oscilloscopes

- Fluke 179 multimeter (MM)

- capacitance meter

- electronic proto-boards

- wire, resistors, capacitors, inductors, diodes, Op-Amps, other ICs

Materials to borrow when necessary

- LTSpice circuit simulation software (on computers in lab)

- lab copy of The Art of Electronics, Horowitz & Hill

- inductance meter

- Keithley voltage supply

Activities

- Read chapter 8 of Horowitz & Hill's The Art of Electronics.

- Read Chapters 10 and 11 of Keith Brindley's eBook Starting Electronics.

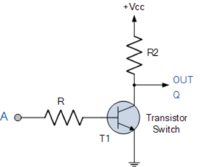

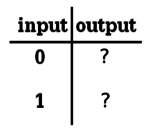

The Inverter or NOT Gate

- Using T1 = TIP31C, R = 10k, R2 = 1k, Vcc = 10VDC construct the circuit shown at the right.

- Apply 0V to input A. What's the output Q?

- Apply 10V to input A. What's the output Q?

- Taking 0 (or close to zero) volts to be logic state "0" and 10 (or close to ten) volts to be logic state "1" construct the logic state truth table for this circuit (see right).

- What type of logic gate does the truth table indicate?

- Letting the input = A and the output = B write a Boolean statement describing this NOT gate (i.e., Q = ???).

We can also use the "True" and "False" representation of digital logic with a "0" state equated with a "False" value and "1" state equated with a "True" value. Yet another digital logic representation is the "High" and "Low" representation equated with the "1" and "0" states respectively.

The OR Gate

- Using two 2N4401BU transistors with R = 10k, R1 = 4.7k and Vcc = 6VDC construct the circuit shown at the right.

- Apply 0V to A and 0V to B. What is Q?

- Apply 1V to A and 0V to B. What is Q?

- Apply 0V to A and 1V to B. What is Q?

- Apply 1V to A and 1V to B. What is Q?

- Construct a truth table for this circuit.

- What type of logic gate does the truth table indicate?

- Letting the input = A and the output = B write a Boolean statement describing this OR gate.

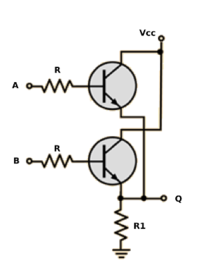

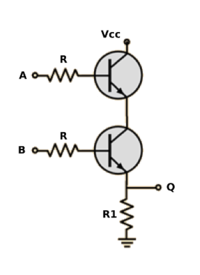

The AND Gate

- Using two 2N4401BU transistors with R = 10k, R1 = 4.7k and Vcc = 6VDC construct the circuit shown at the right.

- Apply 0V to A and 0V to B. What is Q?

- Apply 1V to A and 0V to B. What is Q?

- Apply 0V to A and 1V to B. What is Q?

- Apply 1V to A and 1V to B. What is Q?

- Construct a truth table for this circuit.

- What type of logic gate does the truth table indicate?

- Letting the input = A and the output = B write a Boolean statement describing this AND gate.

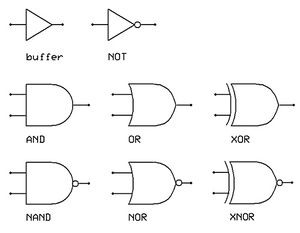

The NOR, NAND, XOR and XNOR Gates

It should be clear that we could follow the OR gate with a NOT gate and get a NOT OR gate (a NOR gate).

We could follow an AND gate with a NOT gate and get a NOT AND gate (a NAND gate).

In addition, there are other basic gates like the XOR (exclusive OR) and the XNOR (exclusive NOR).

An OR gate outputs "True" when either (or both) of its inputs is "True". However, an XOR gate outputs True (we'll drop the quotes) when either of its inputs is True (but not both). The XNOR gate is a combination of an XOR gate and an inverter (a NOT XOR gate).

Digital ICs

It would be extremely tedious (though in principle possible) to build every logic circuit from discrete transistor elements. There are dedicated digital ICs that perform these logic functions reducing cost, saving time and generally making it easier to build complex digital circuits.

- The 7400 series digital ICs. These are robust TTL (transistor-transistor logic) devices and operate at 5V.

- The 4000 series digital ICs. These are (slightly less robust) CMOS devices and operate over a range of voltages.

Bistable Circuits - Flip-Flops - Digital Memory

The type of logic gates examined above are known as combinational (or time independent) logic gates. That is, their output is a function (only) of their present combined inputs. This means that combinational logic has no memory.

For a circuit to have memory its output must depend not only on its present input but also on its past input. Logic of this type is known as sequential logic. Virtually all circuits in practical digital devices are a mixture of combinational and sequential logic.

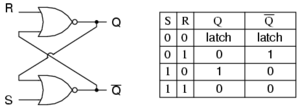

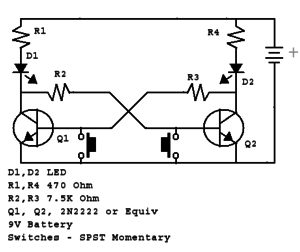

The SR-Type NOR Bistable or Latch

Recall that the NOR gate is an inverting OR gate. Also recall that an OR gate's output is High when either or both of its inputs is High. So, a NOR gate's output is High when both its inputs are Low and its output is Low for all else.

Now consider the NOR latch symbolic circuit shown at the right with both S and R initially Low (S and R stand for Set and Reset respectively). If S then goes High the output of S-gate is Low. And since the output of the S-gate is cross-coupled to the input of the R-gate the R-gate is High. This High from the R-gate output is then fed back into the S-gate input keeping the S-gate output low.

Now consider what happens when S subsequently goes Low. Since the input to the S-gate is now still a combination of a Low and a High its output is still Low. That is, the output is "latched" Low and Q is "latched" High regardless of subsequent changes in S. The outputs "remember" their states. The analysis remains valid when R and S are switched.

- Using a proto-board, two 2N4401BU transistors and LEDs build the flip-flop circuit shown at the right.

- Verify the S-R NOR latch function table.